# 100Gb/s QSFP56 SR2 850nm 100m MMF Optical Transceiver

#### **Features**

- Hot-pluggable QSFP56 form factor

- Compliant to SFF-8636

- Maximum link length of 100m on 0M4 fiber with KP4 FEC

- +3.3V single power supply

- Power dissipation < 3.5W

- Operating case temp Commercial: 0°C to +70 °C

- MPO-12 APC connector

- RoHS compliant

#### **Description**

The QSFP56 100G SR2 optical module utilizes a 2x50G PAM4 channel design, supporting 100Gbps aggregate bandwidth and a transmission distance of up to 70-100 meters (0M4 fiber). It features low power consumption and low latency, and complies with IEEE 802.3 standards. This module is commonly used for short-distance, high-speed interconnects in data centers and is suitable for use in 200GbE to 2x100G applications, enabling flexible bandwidth deployment and interconnect expansion.

The product is designed with form factor, optical/electrical connection and digital diagnostic interface according to the QSFP56 Multi-Source Agreement (MSA). It has been designed to meet the harshest external operating conditions including temperature, humidity and EMI interference.

#### **Functional Description**

The module incorporates 2 parallel channels, on 850nm Center Wavelength, operating at 50G per channel. The transmitter path incorporates a 2-channel re-timer, a quad channel VCSEL drivers together with a VCSEL array. On the receiver path, a photo diode array optics are coupled with an 2- channel re-timer. The electrical interface is compliant with IEEE 802.3bs and QSFP56 MSA in the transmitting and receiving directions, and the optical interface is compliant to QSFP56 MSA with MPO-12 APC Optical Connector.

A single +3.3V power supply is required to power up this product. All the power supply pins are internally connected and should be applied concurrently. As per MSA specifications the module offers seven low speed hardware control pins (including the 2-wire serial interface): ModSelL, SCL, SDA, ResetL, InitMode, ModPrsL and IntL.

Module Select (ModSelL) is an input pin. When held low by the host, this product responds to 2-wire serial communication commands.

The ModSelL allows the use of this product on a single 2-wire interface bus — individual ModSelL lines must be used.

Module Select (ModSelL) is an input pin. When held low by the host, this product responds to 2-wire serial communication commands. The ModSelL allows the use of this product on a single 2-wire interface bus — individual ModSelL lines must be used.

Serial Clock (SCL) and Serial Data (SDA) are required for the 2-wire serial bus communication interface and enable the host to access the memory map.

The ResetL pin enables a complete reset, returning the settings to their default state, when a low level on the ResetL pin is held for longer than the minimum pulse length. During the execution of a reset the host shall disregard all status bits until it indicates a completion of the reset interrupt. The product indicates this by posting an IntL (Interrupt) signal with the Data\_Not\_Ready bit negated in the memory map. Note that on power up (including hot insertion) the module should post this completion of reset interrupt without requiring a reset.

Initialize Mode (InitMode) is an input signal. It is pulled up to Vcc in the QSFP56 module. The InitMode signal allows the host to define whether the QSFP56 module will initialize under host software control (InitMode asserted High) or module hardware control (InitMode deasserted Low). Under host software control, the module shall remain in Low Power Mode until software enables the transition to High Power Mode, as defined in the QSFP56 Management Interface Specification. Under hardware control (InitMode de-asserted Low), the module may immediately transition to High Power Mode after the management interface is initialized. The host shall not change the state of this signal while the module is present. In legacy QSFP applications, this signal is named LPMode. See SFF-8679 for LPMode signal description.

Module Present (ModPrsL) is a signal local to the host board which, in the absence of a product, is normally pulled up to the host Vcc. When the product is inserted into the connector, it completes the path to ground through a resistor on the host board and asserts the signal. ModPrsL then indicates its present by setting ModPrsL to a "Low" state.

Interrupt (IntL) is an output pin. "Low" indicates a possible operational fault or a status critical to the host system. The host identifies the source of the interrupt using the 2-wire serial interface. The IntL pin is an open collector output and must be pulled to the Host Vcc voltage on the Host board.

## **Absolute Maximum Ratings**

| Table1-Absolute Maximum Ratings              |         |      |         |      |      |       |  |  |  |  |

|----------------------------------------------|---------|------|---------|------|------|-------|--|--|--|--|

| Parameter                                    | Symbols | Min. | Typical | Max. | Unit | Notes |  |  |  |  |

| Storage Temperature                          | TSTG    | -40  |         | +85  | °C   |       |  |  |  |  |

| Operating Relative Humidity (non-condensing) | RH      | +5   |         | 85   | %    | 1     |  |  |  |  |

| Supply Voltage                               | VCC     | -0.5 |         | 3.6  | V    |       |  |  |  |  |

| Receiver Damage<br>Threshold per Lane        | PRDMG   | 5    |         |      | dBm  |       |  |  |  |  |

Notes:

[1] No condensation

## **Recommended Operating Conditions**

| Table2-Recommended Operating Conditions |                      |       |      |       |                         |   |  |  |  |  |

|-----------------------------------------|----------------------|-------|------|-------|-------------------------|---|--|--|--|--|

| Parameter                               | Symbols Min. Typical |       | Max. | Unit  | Notes                   |   |  |  |  |  |

| Case Temperature                        | Тс                   | 0     |      | +70   | $^{\circ}\! \mathbb{C}$ |   |  |  |  |  |

| Supply Voltage                          | VCC                  | 3.135 | 3.3  | 3.465 | V                       |   |  |  |  |  |

| Power Dissipation                       | Pd                   |       |      | 3.5   | W                       |   |  |  |  |  |

| Data Rate                               |                      |       |      | 212.5 | Gbps                    |   |  |  |  |  |

| Link Distance with G.652                | D                    |       |      | 100   | m                       | 1 |  |  |  |  |

Notes:

[1]OM4 fiber, 70m for OM3 fiber, with KP4 FEC

#### **Electrical Characteristic**

| Table3-Electrical Characteristic         |             |                   |         |      |      |       |  |  |  |  |  |  |

|------------------------------------------|-------------|-------------------|---------|------|------|-------|--|--|--|--|--|--|

| Parameter                                | Symbol      | Min.              | Typical | Max. | Unit | Notes |  |  |  |  |  |  |

| Transmitter                              |             |                   |         |      |      |       |  |  |  |  |  |  |

| Signaling rate (each lane)               | SR          | 26.5625 ± 100 ppm |         |      | GBPS |       |  |  |  |  |  |  |

| Differential data input voltage per lane | Vin,pp,diff | 900               |         |      | mV   |       |  |  |  |  |  |  |

| Differential termination mismatch        |             |                   |         | 10   | %    |       |  |  |  |  |  |  |

| Single-ended voltage tolerance range     |             | -0.4              |         | 3.3  | V    |       |  |  |  |  |  |  |

| DC common mode voltage                   |             | -350              |         | 2850 | mV   |       |  |  |  |  |  |  |

| Receiver                                 |             |                   |         |      |      |       |  |  |  |  |  |  |

| Signaling rate (each lane)              | SR | 2     | 6.5625 ± 100 | ppm  | GBd |  |

|-----------------------------------------|----|-------|--------------|------|-----|--|

| Differential output voltage             |    |       |              | 900  | mV  |  |

| Near-end ESMW (Eye symmetry mask width) |    | 0.265 |              |      | UI  |  |

| Near-end Eye height, differential (min) |    | 70    |              |      | mV  |  |

| Far-end ESMW (Eye symmetry mask width)  |    | 0.2   |              |      | UI  |  |

| Far-end Eye height, differential (min)  |    | 30    |              |      | mV  |  |

| Differential termination mismatch       |    |       |              | 10   | %   |  |

| Transition time (min, 20% to 80%)       |    | 9.5   |              |      | ps  |  |

| DC common mode voltage                  |    | -350  |              | 2850 | mV  |  |

## **Optical Characteristics**

| Parameter                                                             | Symbols | Units.   | Min. | Typical   | Max               | Notes |  |  |  |  |  |

|-----------------------------------------------------------------------|---------|----------|------|-----------|-------------------|-------|--|--|--|--|--|

| Transceiver                                                           |         |          |      |           |                   |       |  |  |  |  |  |

| Signaling rate (each lane)                                            | SR      | GBd      |      | 26.5625 ± | 100 ppm           |       |  |  |  |  |  |

| Modulation format                                                     | -       | -        |      | PAI       | M4                |       |  |  |  |  |  |

| Lane wavelength                                                       | λ       | nm       | 840  | 850       | 860               |       |  |  |  |  |  |

| RMS spectral width                                                    | Δλ      | nm       | -    | -         | 0.6               |       |  |  |  |  |  |

| Average launch power, each lane                                       | -       | dBm      | -6.5 | -         | 4                 |       |  |  |  |  |  |

| Outer Optical Modulation Amplitude [OMA <sub>outer</sub> ], each lane | -       | dBm      | -4.5 | -         | 3                 | 1     |  |  |  |  |  |

| Launch power in OMA <sub>outer</sub> minus TDECQ, each lane           | -       | dBm      | -5.9 | -         | -                 |       |  |  |  |  |  |

| Transmitter and dispersion eye closure for PAM4 (TDECQ), each lane    | -       | dB       | -    | -         | 4.5               |       |  |  |  |  |  |

| Average launch power of OFF transmitter, each lane                    | -       | dBm      | -    | -         | -30               |       |  |  |  |  |  |

| Extinction ratio                                                      | -       | dB       | 3    | -         | -                 |       |  |  |  |  |  |

| Transmitter transition time, each lane                                | -       | ps       | -    | -         | 34                |       |  |  |  |  |  |

| Optical return loss tolerance                                         | -       | dB       | -    | -         | 12                |       |  |  |  |  |  |

|                                                                       |         | Receiver |      |           |                   |       |  |  |  |  |  |

| Signaling rate (each lane)                                            | SR      | GBd      |      | 26.5625 ± | 100 ppm           |       |  |  |  |  |  |

| Modulation format                                                     | -       | -        |      | PAI       | M4                |       |  |  |  |  |  |

| Lane wavelength                                                       | λ       | nm       | 840  | 850       | 860               |       |  |  |  |  |  |

| Damage threshold, each lane                                           | PIN     | dBm      | 5    | -         | -                 |       |  |  |  |  |  |

| Average receive power, each lane                                      | -       | dBm      | -8.4 | -         | 4                 |       |  |  |  |  |  |

| Receive power (OMA <sub>outer</sub> ), each lane                      | -       | dBm      | -    | -         | 3                 |       |  |  |  |  |  |

| Receiver sensitivity (OMA <sub>outer)</sub> , each lane               | -       | dBm      | -    | -         | Max(6.5,SECQ-7.9) | 2     |  |  |  |  |  |

| LOS Assert     | - | dBm | -30 | - | -10 |  |

|----------------|---|-----|-----|---|-----|--|

| LOS De-Assert  | - | dBm | -   | - | -9  |  |

| LOS Hysteresis | - | dB  | 0.5 | - | -   |  |

Notes:

[1] Even if the TDECQ < 1.4 dB, the OMA $_{outer}$  (min) must exceed this value.

[2] Bit Error Ratio  $< 2.4x10^{-4}$ , Pattern PRBS31Q

#### **Pin Description**

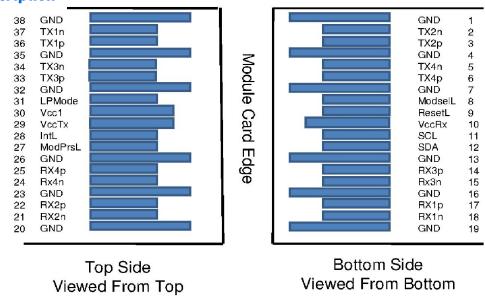

Figure 1 Pin view

#### **Pin Function Definitions**

| Table5-Pin Function Definitions |         |                                     |       |  |  |  |  |  |

|---------------------------------|---------|-------------------------------------|-------|--|--|--|--|--|

| Pin                             | Symbols | Description                         | Notes |  |  |  |  |  |

| 1                               | GND     | Ground                              | 1     |  |  |  |  |  |

| 2                               | Tx2n    | Transmitter Inverted Data Input     |       |  |  |  |  |  |

| 3                               | Tx2p    | Transmitter Non-Inverted Data Input |       |  |  |  |  |  |

| 4                               | GND     | Ground                              | 1     |  |  |  |  |  |

| 5                               | Tx4n    | Transmitter Inverted Data Input     |       |  |  |  |  |  |

| 6                               | Tx4p    | Transmitter Non-Inverted Data Input |       |  |  |  |  |  |

| 7                               | GND     | Ground                              |       |  |  |  |  |  |

| 8                               | ModSelL | Module Select                       |       |  |  |  |  |  |

| 9                               | ResetL  | Module Reset                        |       |  |  |  |  |  |

| 10                              | Vcc Rx  | +3.3V Power Supply Receiver         | 2     |  |  |  |  |  |

| 11                              | SCL     | 2-wire serial interface clock       |       |  |  |  |  |  |

| 12                              | SDA     | 2-wire serial interface data        |       |  |  |  |  |  |

| 13                              | GND     | Ground                              |       |  |  |  |  |  |

| 14                              | Rx3p    | Receiver Non-Inverted Data Output   |       |  |  |  |  |  |

| 15 | Rx3n    | Receiver Inverted Data Output       |   |

|----|---------|-------------------------------------|---|

| 16 | GND     | Ground                              | 1 |

| 17 | Rx1p    | Receiver Non-Inverted Data Output   |   |

| 18 | Rx1n    | Receiver Inverted Data Output       | 1 |

| 19 | GND     | Ground                              | 1 |

| 20 | GND     | Ground                              |   |

| 21 | Rx2n    | Receiver Inverted Data Output       |   |

| 22 | Rx2p    | Receiver Non-Inverted Data Output   |   |

| 23 | GND     | Ground                              |   |

| 24 | Rx4n    | Receiver Inverted Data Output       |   |

| 25 | Rx4p    | Receiver Non-Inverted Data Output   |   |

| 26 | GND     | Ground                              | 1 |

| 27 | ModPrsL | Module Present                      |   |

| 28 | IntL    | Interrupt                           |   |

| 29 | VccTx   | +3.3V Power supply transmitter      | 2 |

| 30 | Vcc1    | +3.3V Power supply                  | 2 |

| 31 | LPMode  | Low Power Mode                      |   |

| 32 | GND     | Ground                              | 1 |

| 33 | ТхЗр    | Transmitter Non-Inverted Data Input |   |

| 34 | Tx3n    | Transmitter Inverted Data Input     |   |

| 35 | GND     | Ground                              | 1 |

| 36 | Tx1p    | Transmitter Non-Inverted Data Input |   |

| 37 | Tx1n    | Transmitter Inverted Data Input     |   |

| 38 | GND     | Ground                              | 1 |

Notes:

[1]Circuit ground is internally isolated from chassis ground.

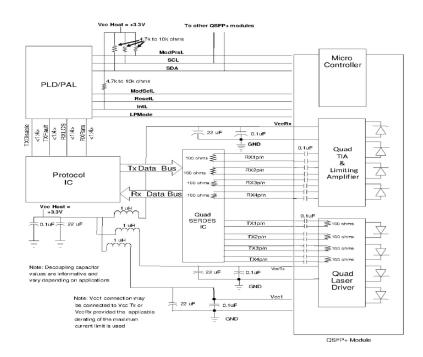

#### **Recommended Interface Circuit**

Figure 2 Recommended Interface Circuit

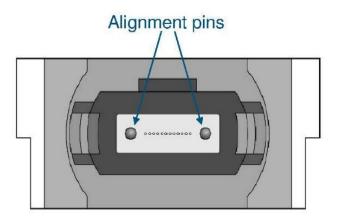

## **Optical interface arrangement**

Transmit Channels: 1 2 3 4

Unused positions: x x x x

Receive Channels: 4 3 2 1

Figure 3 Optical interface arrangement

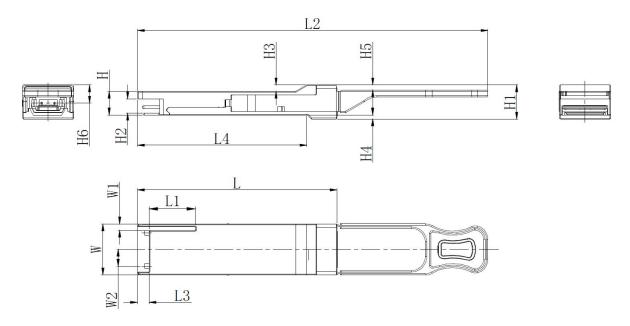

#### **Mechanical Dimensions**

Figure 4 Mechanical Outline

#### Unit mm

|      | L    | L1   | L2  | L3   | L4   | W     | W1  | W2  | Н   | H1   | H2   | Н3  | H4  | H5  | Н6   |

|------|------|------|-----|------|------|-------|-----|-----|-----|------|------|-----|-----|-----|------|

| Max  | 72.2 | -    | 128 | 4.35 | 61.4 | 18.45 | -   | 6.2 | 8.6 | 12.4 | 5.35 | 2.5 | 1.6 | 2.0 | -    |

| Type | 72.0 | -    | -   | 4.20 | 61.2 | 18.35 | -   | -   | 8.5 | 12.2 | 5.2  | 2.3 | 1.5 | 1.8 | 6.55 |

| Min  | 68.8 | 16.5 | 124 | 4.05 | 61.0 | 18.25 | 2.2 | 5.8 | 8.4 | 12.0 | 5.05 | 2.1 | 1.3 | 1.6 | -    |

#### **Warnings**

Handling Precautions: This device is susceptible to damage as a result of electrostatic discharge (ESD).

A static free environment is highly recommended. Follow guidelines according to proper ESD procedures.

#### **Laser Safety**

Radiation emitted by laser devices can be dangerous to human eyes. Avoid eye exposure to direct or indirect radiation.

## Further Information:

Web www.naddod.com

Email For order requirements: sales@naddod.com For cooperation: agency@naddod.com

For customer service: support@naddod.com For other info@naddod.com

For technical support: tech@naddod.com

## Disclaimer

- 1. We are committed to continuous product improvement and feature upgrades, and the contents contained in this manual are subject to change without notice.

- 2. Nothing herein should be construed as constituting an additional warranty.

- 3. NADDOD assumes no responsibility for the use or reliability of equipment or software not provided by NADDOD. Copyright © NADDOD.COM All Rights

NADDOD - Building an Intelligent World with Everything Connected Accelerated AI Clusters | HPC Datacenter | Enterprise Networking